Will Generative AI Play a Leading Role in Chip Design and Manufacturing?

Sep 17, 2024

Will Generative AI Play a Leading Role in Chip Design and Manufacturing?

As in previous years, AI is a big topic in the semiconductor EDA IP chip design space. This year, though, many experts see clear challenges that must be overcome before the technology becomes mainstream. However, those companies that successfully address these issues early on will gain a crucial advantage in improving chip designer productivity and innovation on both existing products and the emerging market of 3DIC and chiplet designs.

To learn more about these AI challenges, Design News asked experts from the EDA IP, systems, and standards spaces: Lu Dai, chair of Accellera Standards; Joe Costello, CEO of Metrics; Manuel Rei, semiconductor solution experience director at Dassault Systèmes; a Microsoft spokesperson; Eric Beyne, senior fellow at imec; Mayank Bhatnagar, director of product marketing in the Silicon Solutions Group at Cadence; and Arif Khan, senior product marketing group director at Cadence. The following is an edited version of their responses.

What real change is generative AI bringing to the EDA IP design and manufacturing?

Lu Dai, Accellera: EDA tools that are heavy in iterative optimization, including many compute-heavy backend flows and some front-end simulations, are a natural fit for AI. Interestingly, compute-heavy flows that were previously deemed good but were unable to be finished before tape out will again be considered. Disruptive technologies will level the playing field and give startups a chance that hasn’t been there for the past twenty years. Finally, China may have a potential AI advantage due to its access to data sets that are not under typical privacy standards.

Joe Costello, Metrics: AI/ML has had a long-term impact on EDA and will continue to have a big impact. As for generative AI and EDA IP design, there is a lot of buzz and hype, but I certainly don't think that, in the near term, it will have the impact that people are promoting or hoping for. High school students will not be developing IP blocks with natural language descriptions of what they want. There are a couple of reasons.

Firstly, generative AI requires a huge amount of data for training. Where are you going to get all this data for EDA IP? Most EDA IPs are proprietary, and the details are encrypted. Some have argued that you could train for EDA IP on open-source designs. No way. There are not enough of them, and they need to be better. The next idea is to limit it to the designs within a single company so you don't run into proprietary issues. That sounds good, but most companies need more designs for generative AI training.

Secondly, EDA IP design is a precision sport. Close enough is not even close. Hopefully, people thinking about this idea have used generative AI for writing or graphics. What these tools can create is impressive. But the problem is that even for graphics, while producing impressive output, it is tough to get exactly what I want. In doing IP design, it must be precisely correct, and so far, that is not possible.

Manuel Rei, Dassault Systèmes: Generative AI is revolutionizing EDA IP design and manufacturing by automating and optimizing complex tasks traditionally handled manually. It accelerates design cycles through automated layout synthesis, circuit design, and optimization, reducing time-to-market for new semiconductor products. AI-driven design exploration enables the discovery of innovative architectures and circuit topologies that enhance performance metrics like power efficiency and speed. By predicting and preventing design errors early, AI models improve reliability and minimize costly rework during manufacturing.

Moreover, AI enhances customization by tailoring designs to specific requirements without sacrificing performance. It boosts simulation and verification processes by automating test case generation and enhancing failure analysis accuracy. AI-powered analytics optimize the supply chain by predicting demand fluctuations, managing inventory efficiently, and identifying manufacturing bottlenecks. Regarding intellectual property, AI aids in generating and protecting designs while facilitating collaboration among global design teams through real-time insights and collaborative tools.

Microsoft Spokesperson: AI can dramatically improve designer productivity—Nvidia already cites ~25% gains from just two initial copilots focusing on documentation and bug characterization. Further, it automates iterative processes—there are many single- or multi-tool loops around different design representations (behavior, RTL, gates, layout) that currently rely heavily on grad school-level acquired knowledge, human experience, intuition, and knowledge of previous designs. GenAI is uniquely good at absorbing this information and can become an indispensable assistant to the engineers, backfilling the workforce shortages.

Arif Khan, Cadence Design Systems: Several key market trends are driving HPC and AI and the demand for newer SoC, chip-to-chip, and module architectures that address the needs of this space. As the need for performance and computation capability increases, standards bodies and IP implementers provide solutions, specifically standards in memory such as the latest LPDDR and HBM versions along with essential interface standards such as 112G/224G, PCIe, and CXL, and chiplet and die-to-die interfaces such as UCIe that are critical to these new architectures for HPC and AI products.

What is necessary for chiplets/3D-ICs to take off in the chip market?

Dai: A diverse library enabling SOC development is needed, as companies interested in chiplets are mostly specialty IP vendors. Compatibility among major foundries is also needed for a standard-based 3D-IC interface. Finally, it’s important not to assume everything should be solved with chiplets. Designers should utilize complexity-based SOC chiplet designs to solve some technology challenges before going after the IP chiplet market.

Rei: Standardization of interconnects and design methodologies are essential for compatibility and ease of integration requirements for chiplet and 3D-IC designs to gain traction in the chip market. Advanced packaging technologies, such as through-silicon vias (TSVs) and effective thermal management, are necessary to support high-density interconnections and manage heat dissipation. Enhanced electronic design automation (EDA) tools are crucial for addressing the complexities of multi-die integration, and improved verification and testing methods are needed to ensure reliability.

A robust manufacturing ecosystem, including foundries and OSATs, and effective supply chain coordination are essential to support production. Achieving economies of scale in chiplet production and developing cost-effective packaging solutions will help make these technologies competitive with traditional designs.

Clear IP management and licensing frameworks are also necessary to encourage collaboration and innovation. Ensuring compliance with regulatory standards, particularly in industries like automotive and healthcare, is also essential.

Microsoft spokesperson: True 3DICs are still largely experimental and not readily accessible to the ASIC/SoC designers. 2.5D will be the next realistic jump, but only so many tools are currently available. 2.5D heterogeneous integration (HI) with active interposers will be the chipset-based alternative offering many benefits of a high degree of integration via more management divide-and-conquer strategies; however, there is little explicit EDA support for HI outside of signal integrity analysis.

Other areas needed for chiplet tech to take off are standards for interconnects, secure data, and collaboration solutions to share die/wafer-level data for interposer design.

Eric Beyne, imec: For chiplets to become a main-stream tech, they must be able to be placed close together in one package to ensure fast, high-bandwidth electrical connections between them—just like the functions in monolithic SoCs. Achieving such closeness depends upon which 3D system integration platform is used: 2.5D chiplet integration connecting chips side-by-side through a common substrate (also known as an interposer) and 3D-SoC, where the chiplets are stacked on top of each other.

The latter is well suited for high-performance computing applications that require smaller form factors or a higher level of system integration. Instead of establishing sideways connections, chiplets can be stacked on each other, forming a 3D-SoC. This approach does not add additional blocks but rather co-designs the chiplets together and lets them operate as if they would be the same chip.

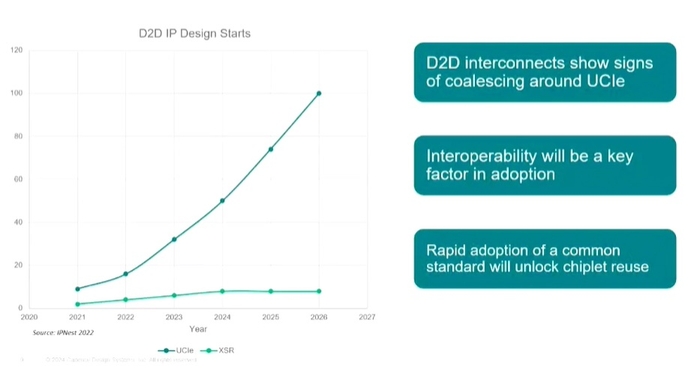

Mayank Bhatnagar, Cadence: Standard interface IP must be established to encourage a chiplet ecosystem for collaboration and innovation. The Universal Chiplet Interconnect Express (UCIe) interface is gaining momentum as chiplet interconnectivity. The UCIe standard for chip die-to-die signal communications has helped heterogeneous chiplet architectures gain support from mainstream commercial chipmakers. The spec is intended to be a common language for chiplets and is designed for a very short distance on a chip's substrate.

Outlook on standards adoption for UCIe and XSR chiplet interfaces. (Source: IP-Nest, used with permission)